Digital interface increases throughput in data-acquisition systems

The Serial Peripheral Interface (SPI), a synchronous serial data protocol used by microcontrollers for communicating with one or more peripheral devices over short distances, has become a de facto standard, widely used in embedded systems.

But the interface, developed by Motorola in the late eighties, may be running out of steam. Today's industrial systems demand extremely high transfer rates between the host and high-resolution, high throughput ADCs; high-resolution data conversion generates more bits of data per sample, while higher throughput provides more samples per second.

To meet the challenge of transmitting data to a host with as little latency as possible and to simplify the many complexities encountered when interfacing with modern MCUs, processors and FPGAs, Texas Instruments has developed multiSPI™, an interface that increases data transfer rates between ADCs and digital hosts, while decreasing the required clock frequency. TI has also announced that multiSPI technology will be present (in various feature sets) on all future TI SAR ADCs.

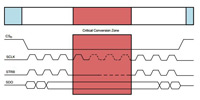

In multiSPI, digital throughput is dramatically increased through the use of 4 data output lines. Or, this feature can be used to decrease the required SPI clock frequency by keeping the throughput constant. Further, multiSPI supports double data rate transfer (DDR), which allows data transfers on both on the rising and falling edge of the SPI clock. Note also that multiSPI retains compatibility with standard SPI communications.

These features are discussed in detail in this whitepaper, with special notes about how each can be applied to different hosts (FPGAs, DSPs or microcontrollers).